The Challenge

In order to make this Verilog program, I adapted the one described at https://numato.com/kb/generating-square-wave-using-fpga/ to the clock frequency of the hardware used in this challenge which it 125Mhz. The counter is so decremented by CLOCK_FREQUENCY/(2*freq/100) converted to integer through $rtoi method.

`timescale 1ns / 1ps

module tone_generator(

input clk,

input rst,

output wave_out,

input [31:0] freq

);

localparam CLOCK_FREQUENCY = 125000000;

// Counter for toggling of clock

reg [31:0] counter;

reg sq_wave_reg = 0;

assign wave_out = sq_wave_reg;

always @(posedge clk) begin

if (rst) begin

counter <= 32'h00;

sq_wave_reg <= 1'b0;

end

else begin

// If counter is zero, toggle sq_wave_reg

if (counter == 32'h00) begin

sq_wave_reg <= ~sq_wave_reg;

counter <= CLOCK_FREQUENCY/2 - 1;

counter <= $rtoi(CLOCK_FREQUENCY/(2*freq/100)) - 1 ;

end

// Else count down

else

counter <= counter - 1;

end

end

endmodule

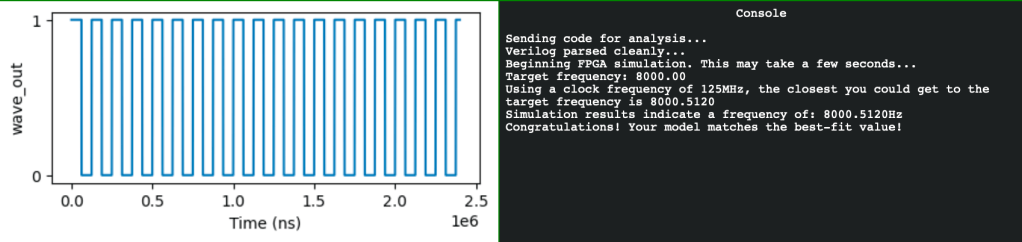

Here are the results of the different tests:

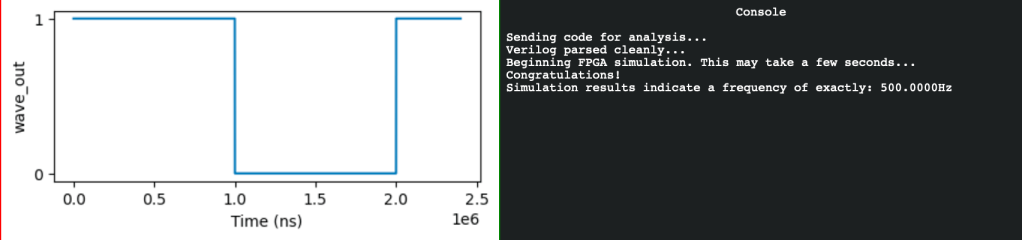

At 500Hz

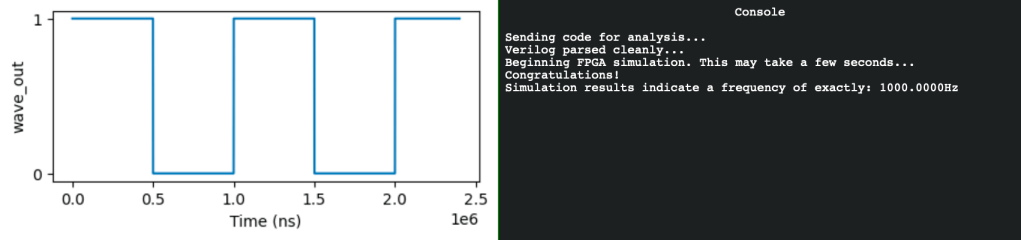

At 1KHz

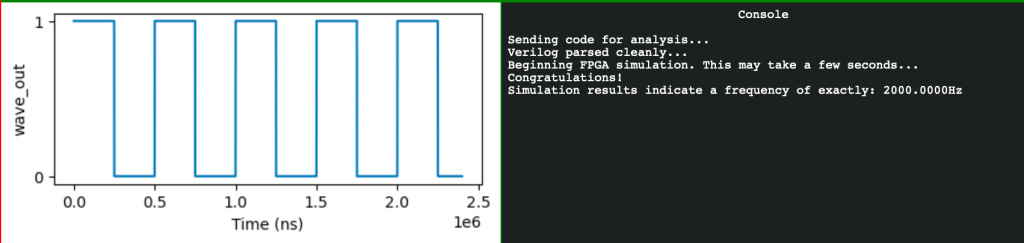

At 2 KHz

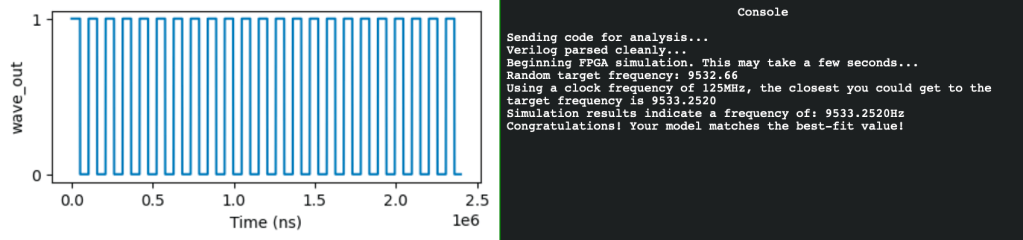

Random Simulation: 9532.66 Hz

8 KHz as a test Input

I was then able to Play Sound and Program Device!